Pin Name A0 ~ A12 BA0 ~ BA1 DQ0 ~ DQ63 CLK0 ~ CLK1 CKE0 ~ CKE1 CS0 ~ CS1 RAS CAS Select bank Data input/output Clock input Clock enable input Chip select input Row address strobe Column address strobe Function Address input (Multiplexed) WE DQM0 ~ 7 VDD VSS SDA SCL DU NC Pin Name Write enable DQM Po.

ge 54-TSOP(II) 54-sTSOP(II)

SDRAM

Height 1,000mil 1,250mil 1,250mil

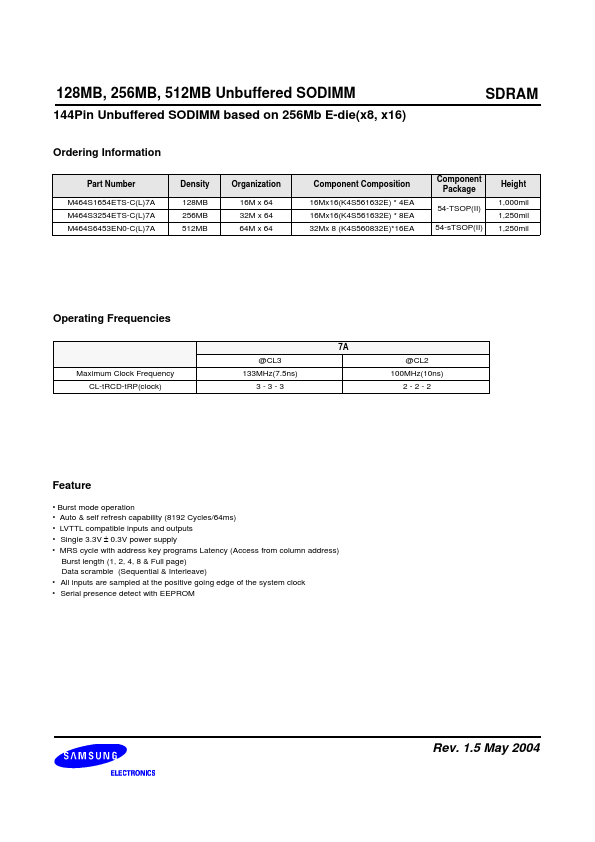

Operating Frequencies

7A @CL3 Maximum Clock Frequency CL-tRCD-tRP(clock) 133MHz(7.5ns) 3-3-3 @CL2 100MHz(10ns) 2-2-2

Feature

• Burst mode operation

• Auto & self refresh capability (8192 Cycles/64ms)

• LVTTL compatible inputs and outputs

• Single 3.3V ± 0.3V power supply

• MRS cycle with address key programs Latency (Access from column address) Burst length (1, 2, 4, 8 & Full page) Data scramble (Sequential & Interleave)

• All inputs are sampled at the positive going edge of the system clock

• Serial presence detect with E.

Similar Product

| No. | Part # | Manufacture | Description | Datasheet |

|---|---|---|---|---|

| 1 | M464S1724DTS |

Samsung semiconductor |

16Mx64 SDRAM SODIMM based on 8Mx16 / 4Banks /4K Refresh / 3.3V Synchronous DRAMs with SPD |

|

| 2 | M464S1724ETS |

Samsung semiconductor |

64MB / 128MB Unbuffered SODIMM |

|

| 3 | M464S1724FTS |

Samsung semiconductor |

144pin Unbuffered SODIMM based on 128Mb F-die 64-bit Non ECC |

|

| 4 | M464S0824DT1 |

Samsung semiconductor |

8Mx64 SDRAM SODIMM based on 4Mx16 |

|

| 5 | M464S0924CT1 |

Samsung semiconductor |

8Mx64 SDRAM SODIMM based on 8Mx16 |

|