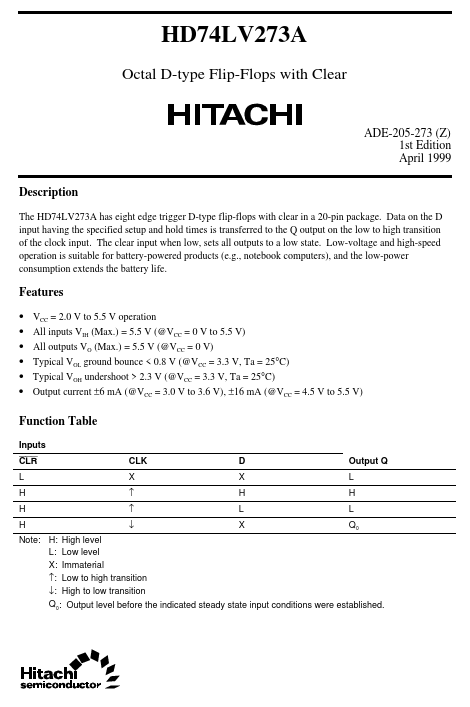

The HD74LV273A has eight edge trigger D-type flip-flops with clear in a 20-pin package. Data on the D input having the specified setup and hold times is transferred to the Q output on the low to high transition of the clock input. The clear input when low, sets all outputs to a low state. Low-voltag.

•

•

•

•

•

• VCC = 2.0 V to 5.5 V operation All inputs VIH (Max.) = 5.5 V (@VCC = 0 V to 5.5 V) All outputs VO (Max.) = 5.5 V (@VCC = 0 V) Typical VOL ground bounce < 0.8 V (@VCC = 3.3 V, Ta = 25°C) Typical VOH undershoot > 2.3 V (@VCC = 3.3 V, Ta = 25°C) Output current ±6 mA (@VCC = 3.0 V to 3.6 V), ±16 mA (@VCC = 4.5 V to 5.5 V)

Function Table

Inputs CLR L H H H CLK X ↑ ↑ ↓ D X H L X Output Q L H L Q0

Note: H: High level L: Low level X: Immaterial ↑: Low to high transition ↓: High to low transition Q0: Output level before the indicated steady state input conditions were established.

HD74LV.

Similar Product

| No. | Part # | Manufacture | Description | Datasheet |

|---|---|---|---|---|

| 1 | HD74LV273A |

Renesas |

Octal D-type Flip-Flops |

|

| 2 | HD74LV27A |

Hitachi Semiconductor |

Triple 3-input Positive NOR Gates |

|

| 3 | HD74LV27A |

Renesas |

Triple 3-input Positive NOR Gates |

|

| 4 | HD74LV20A |

Hitachi Semiconductor |

Dual 4-input Positive NAND Gates |

|

| 5 | HD74LV20A |

Renesas |

Dual 4-input Positive NAND Gates |

|