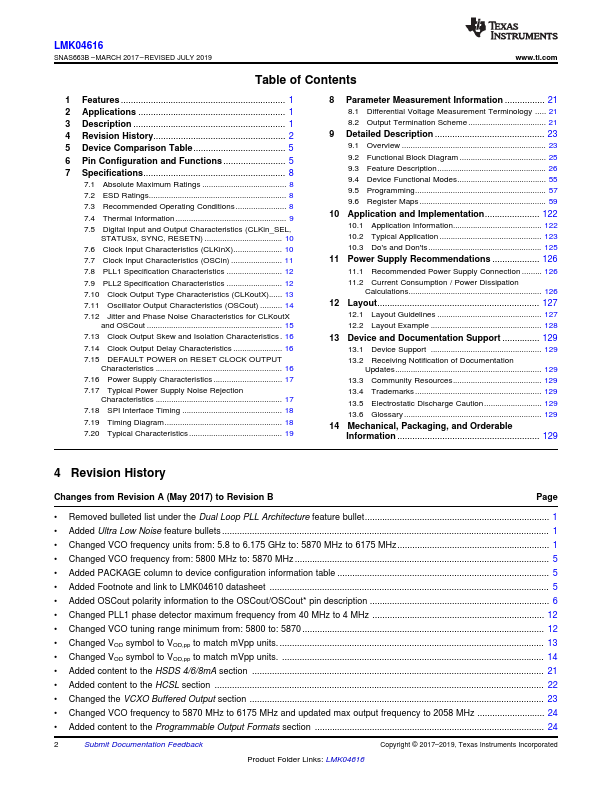

The LMK0461x device family is the industry’s highest performance and lowest power jitter cleaner with JESD204B support. The 16 clock outputs can be configured to drive eight JESD204B converters or other logic devices using device and SYSREF clocks. The 17th output can be configured to provide a sign.

•1 Dual-loop PLL architecture

• Ultra low noise (10 kHz to 20 MHz):

– 48-fs RMS jitter at 1966.08 MHz

– 50-fs RMS jitter at 983.04 MHz

– 61-fs RMS jitter at 122.88 MHz

•

–165-dBc/Hz noise floor at 122.88 MHz

• JESD204B support

– Single shot, pulsed, and continuous SYSREF

• 16 differential output clocks in 8 frequency groups

– Programmable output swing between 700

mVpp to 1600 mVpp

– Each output pair can be configured to

SYSREF clock output

– 16-bit channel divider

– Minimum SYSREF frequency of 25 kHz

– Maximum output frequency of 2 GHz

– Precision digital delay, dynamically adjustable

– Digita.

Similar Product

| No. | Part # | Manufacture | Description | Datasheet |

|---|---|---|---|---|

| 1 | LMK04610 |

Texas Instruments |

Ultra-Low Noise and Low Power JESD204B Compliant Clock Jitter Cleaner |

|

| 2 | LMK04000 |

Texas Instruments |

Family Low-Noise Clock Jitter Cleaner |

|

| 3 | LMK04000 |

National Semiconductor |

Low-Noise Clock Jitter Cleaner |

|

| 4 | LMK04001 |

Texas Instruments |

Family Low-Noise Clock Jitter Cleaner |

|

| 5 | LMK04002 |

Texas Instruments |

Family Low-Noise Clock Jitter Cleaner |

|