Table 1. Pin Description No 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 Name VSSC_AR VDDC_AR R_IN VDDC_PR R_VOUT1 VSSC_PR R_CLPC VDDA_AG VSSA_AG VSSC_AG VDDC_AG G_IN VDDC_PG G_VOUT1 VSSC_PG G_CLPC VDDA_AB VSSA_AB VSSC_AB VDDC_AB B_IN VDDC_PB B_VOUT1 VSSC_PB.

•

•

•

•

•

•

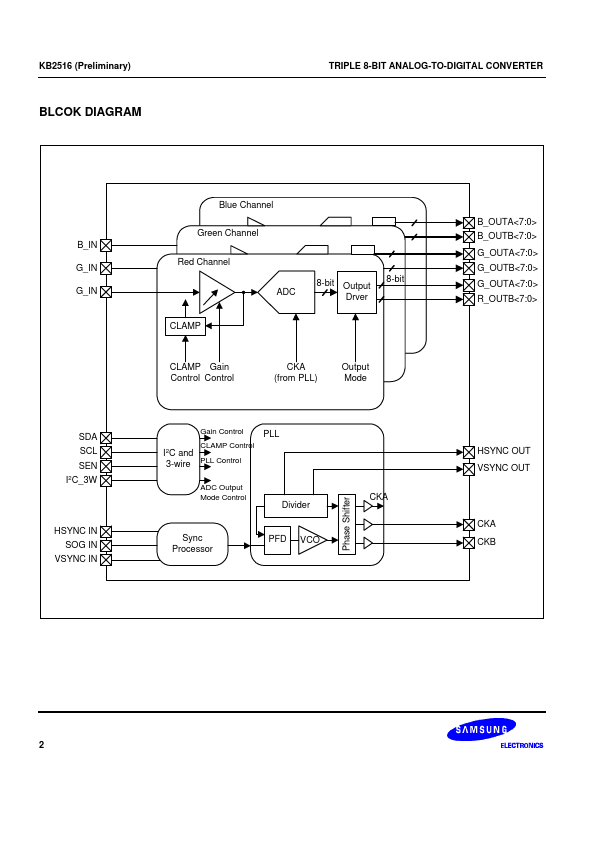

• Analog bandwidth of 500MHz 3 clamps for 256 programmable levels 3 programmable gain amplifiers Analog input range: 0.5Vpp to 1.0Vpp Triple 8-bit ADC Sampling rate up to 140MHz Fully integrated PLL to generate the ADC clock, which can be locked to a HSYNC

•

•

•

•

•

• Integrated PLL divider Programmable clock phase control (Φ step = 7.5°) Integrated SOG separator and HSYNC input polarity detector Single and double pixel width output data bus Support I2C and 3-wire serial interface Power down mode 1.25W power dissipation

ORDERING INFORMATION

Device KB2516 Package 144-LQFP-2020 Orde.

Similar Product