Similar Datasheet

- M54970P 9-Bit Serial Input / Latched Driver - Mitsubishi Electric

- M54972FP Bi-CMOS 8-BIT SERIAL-INPUT LATCHED DRIVER - Mitsubishi

- M54972P Bi-CMOS 8-BIT SERIAL-INPUT LATCHED DRIVER - Mitsubishi

- M54974P Bi-CMOS 12-BIT SERIAL-INPUT LATCHED DRIVER - Mitsubishi

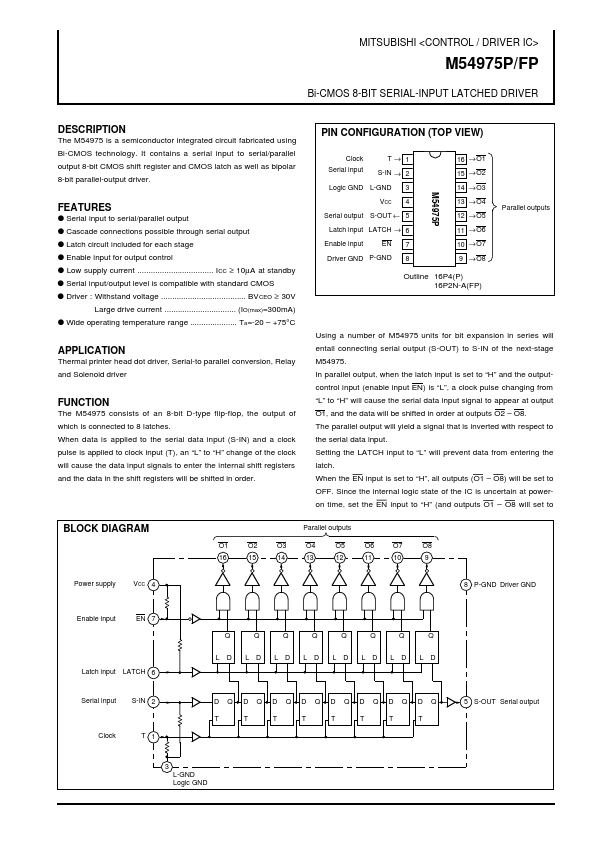

- M54975FP Bi-CMOS 8-BIT SERIAL-INPUT LATCHED DRIVER - Mitsubishi

- M54975P Bi-CMOS 8-BIT SERIAL-INPUT LATCHED DRIVER - Mitsubishi

- M54977P Bi-CMOS 12-BIT SERIAL-INPUT LATCHED DRIVER - Mitsubishi

| @ 2014 :: Datasheetspdf.com :: Semiconductors datasheet search & download site. (Privacy Policy & Contact) |