Similar Datasheet

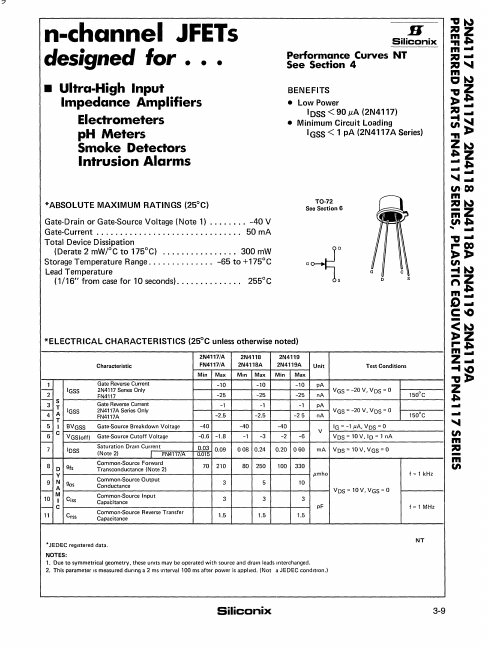

- FN4117 n-channel JFET - Siliconix

- FN4117A ULTRA-HIGH INPUT IMPEDANCE N-CHANNEL JFET - Linear Integrated Systems

- FN4117A n-channel JFET - Siliconix

| @ 2014 :: Datasheetspdf.com :: Semiconductors datasheet search & download site. (Privacy Policy & Contact) |