Similar Datasheet

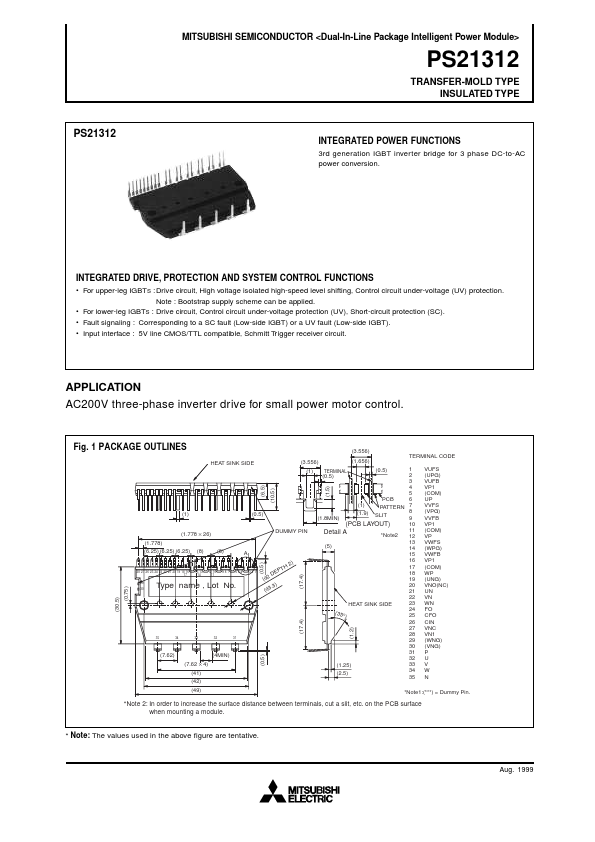

- PS21312 Dual-In-Line Package Intelligent Power-Module - Mitsubishi Electric Semiconductor

- PS21313 Dual-In-Line Package Intelligent Power-Module - Mitsubishi Electric Semiconductor

- PS21342-G Intellimod Module Dual-In-Line Intelligent Power-Module - Powerex Power

- PS21343-N TRANSFER-MOLD TYPE INSULATED TYPE - Mitsubishi Electric Semiconductor

- PS21352-G Intellimod Module Dual-In-Line Intelligent Power-Module - Powerex Power

- PS21353-G Dual-In-Line Intelligent Power Module - Powerex Power Semiconductors

- PS2136 USB 2.0 Flash Controller - PHISON

| @ 2014 :: Datasheetspdf.com :: Semiconductors datasheet search & download site. (Privacy Policy & Contact) |