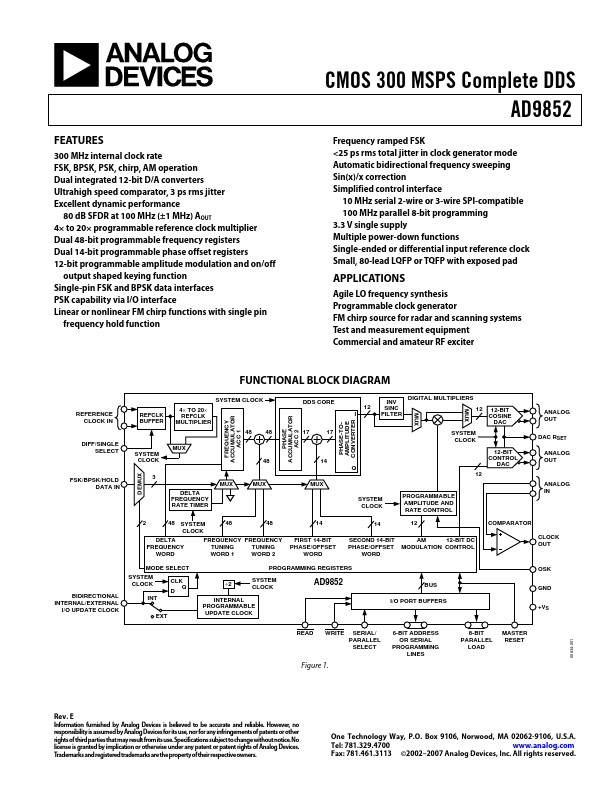

CMOS 300 MHz Complete-DDS

Description

FEATURES

300 MHz internal clock rate FSK, BPSK, PSK, chirp, AM operation Dual integrated 12-bit D/A converters Ultrahigh speed comparator, 3 ps rms jitter Excellent dynamic performance

80 dB SFDR at 100 MHz (±1 MHz) AOUT 4× to 20× programmable reference clock multiplier Dual 48-bit programmable frequency registers Dual 14-bit programmable phase offset regist...

Analog Devices

AD9852

AD9852 PDF File

Similar Datasheet