Phase-Locked Loop Clock Distribution for Synchronous DRAM Applications

Description

HC2510C

HC2510C

Features

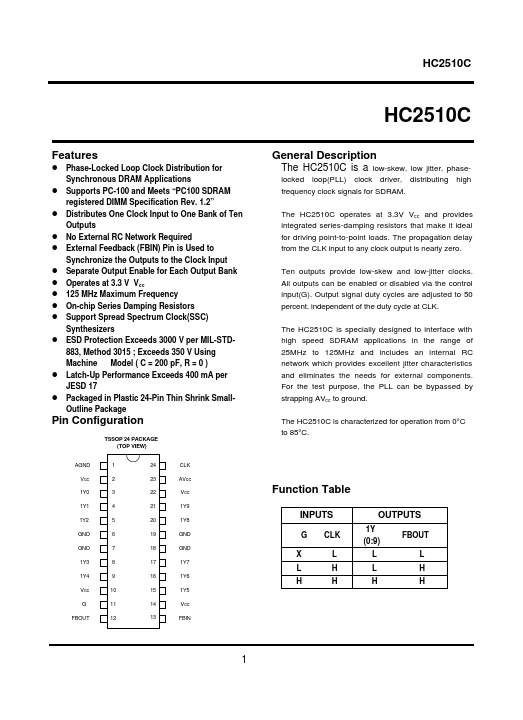

l l l l l l l l l l l Phase-Locked Loop Clock Distribution for Synchronous DRAM Applications Supports PC-100 and Meets “PC100 SDRAM registered DIMM Specification Rev. 1.2” Distributes One Clock Input to One Bank of Ten Outputs No External RC Network Required External Feedback (FBIN) Pin is Used to Synchronize the Outputs to the Cloc...

Hynix Semiconductor

HC2510C

HC2510C PDF File

Similar Datasheet